L’hardware nei prossimi anni si riprenderà il posto che merita sulla frontiera dell’innovazione. Già, perché l’ultimo periodo è stato tutto un parlare di corsa dei modelli AI, ma questa è solo metà della partita che il mondo sta giocando per il futuro.

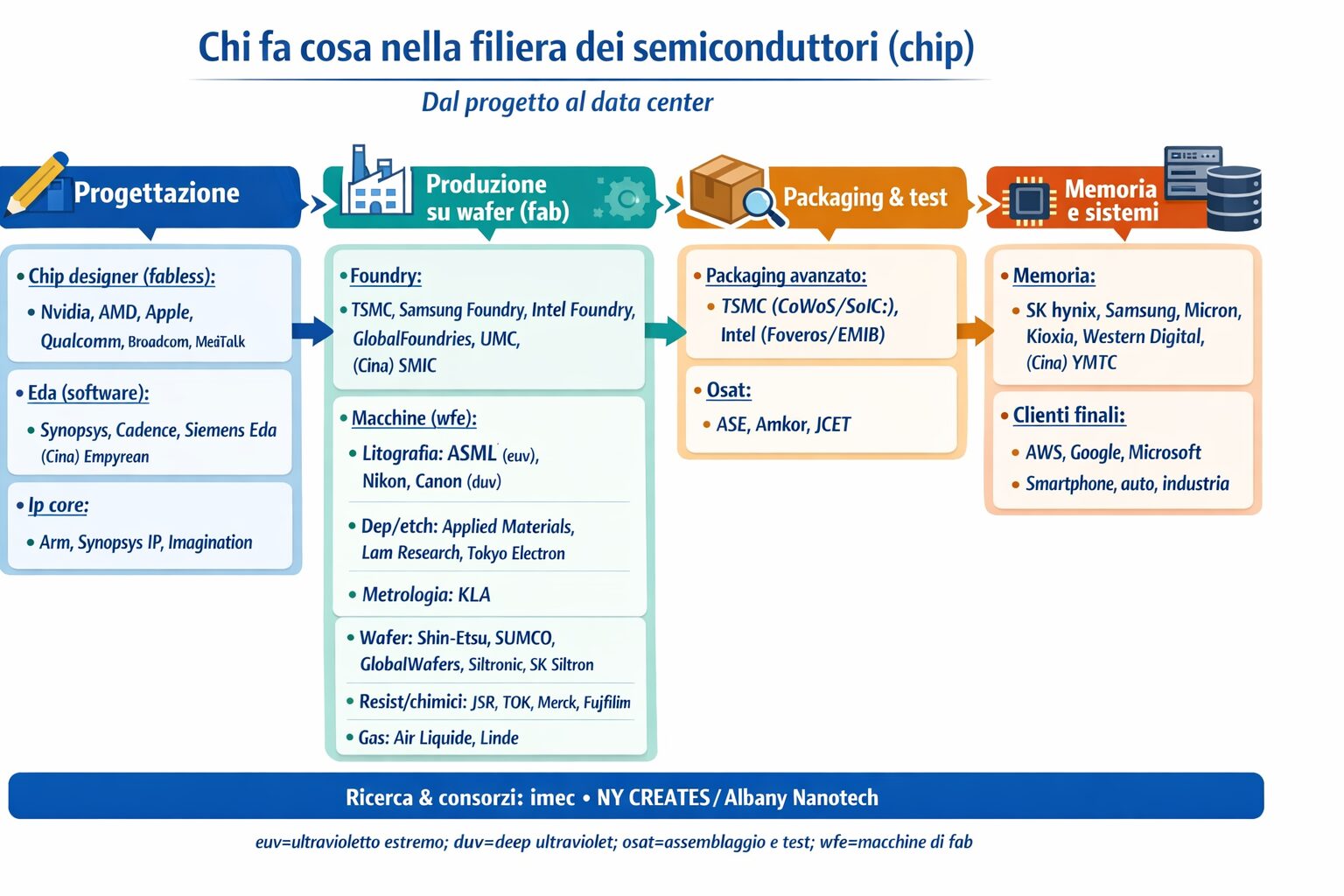

La parte restante è un universo ignorato dai più e che fa da fondamenta a tutto, ossia i chip e i sistemi di produzione correlati. Tantissimi soggetti stanno investendo miliardi per superare gli attuali limiti e quindi poter avere chip più potenti, senza i quali risulta difficile avere una AI di livello superiore.

In particolare, per i chip destinati all’AI, il vincolo principale è sempre più l’energia: la metrica che guida investimenti e scelte tecnologiche è la performance per watt.

Dentro questo quadro, i produttori stanno costruendo una cassetta degli attrezzi fatta di evoluzioni incrementali già vicine alla produzione e di scommesse che mirano a superare i limiti delle attuali tecnologie di “stampa dei chip”.

Ora basate su litografia EUV (Extreme Ultraviolet – Ultravioletto Estremo, una tecnologia avanzata di produzione di semiconduttori che utilizza una lunghezza d’onda di per stampare circuiti microscopici sui wafer di silicio). Essenziale per chip a 7 nm (nanometri), 5 nm, 3 nm e inferiori, è dominata dall’olandese ASML.

Oppure si cerca di superare i limiti del silicio, con nuovi materiali.

Indice degli argomenti:

Chip e litografia, cosa sono davvero

Prima di tutto, è bene sapere che un chip non è un “pezzo unico” scavato nel silicio. È un edificio a molti piani: strati di materiale conduttivo e isolante, con milioni o miliardi di interruttori (i transistor) e i minuscoli “fili” che li collegano. Per costruire questi strati si usa la fotolitografia, che si può immaginare come una stampa di precisione.

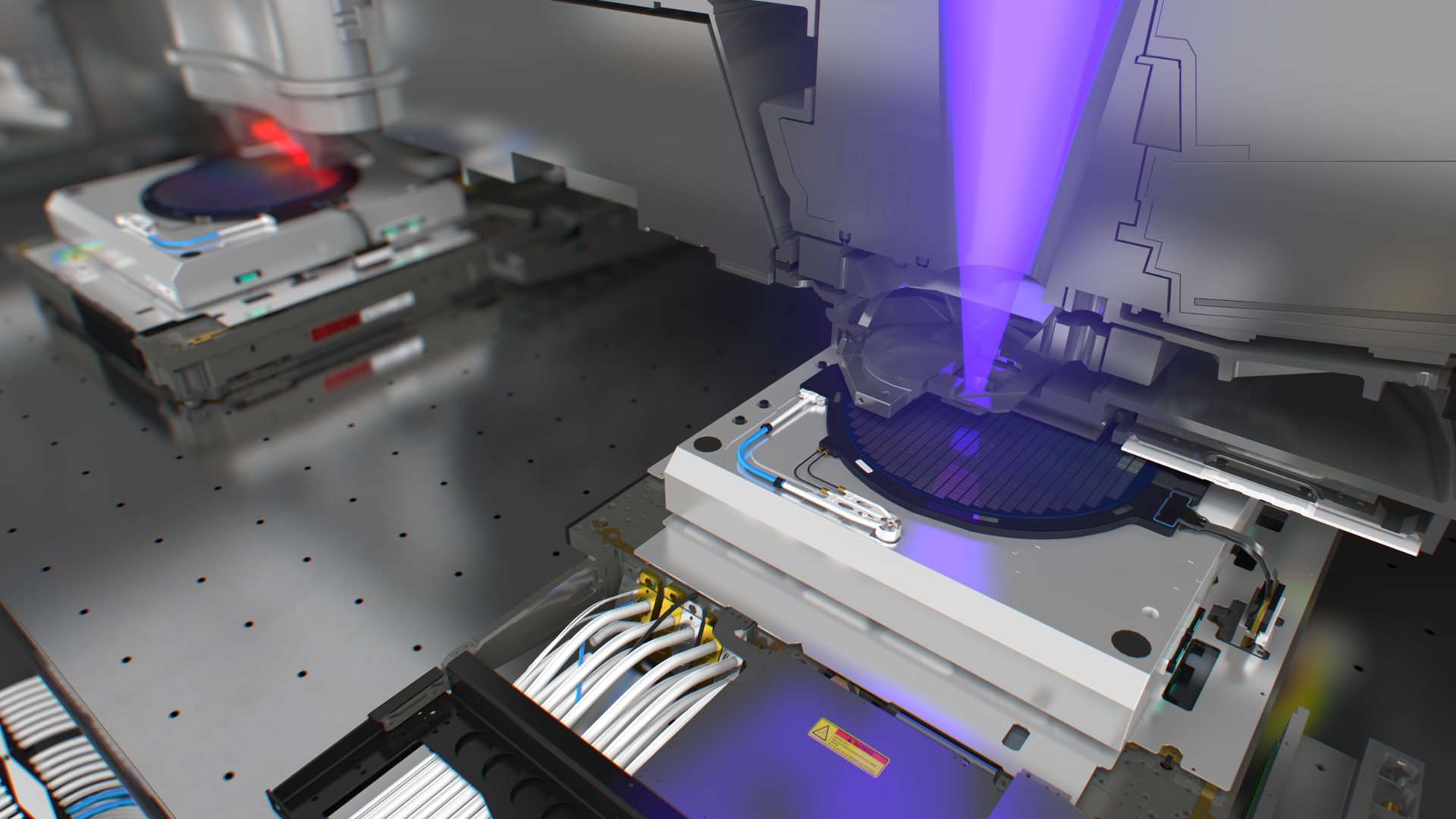

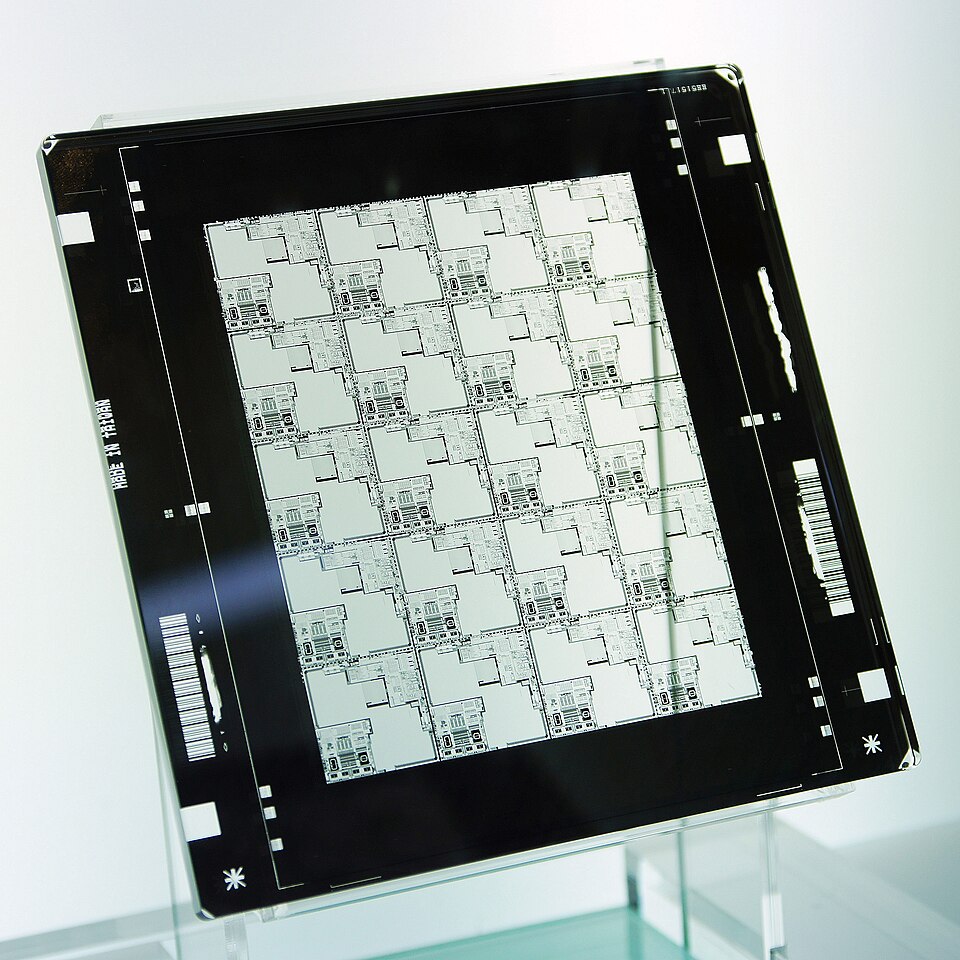

Il principio è simile a quello di una vecchia camera oscura: un fascio di luce attraversa una “maschera” (un po’ come uno stencil con il disegno del circuito) e proietta l’immagine su un wafer di silicio coperto da un materiale fotosensibile chiamato photoresist. Dove arriva la luce, la chimica del resist cambia; poi, con passaggi successivi, quel disegno viene trasferito nello strato sottostante. Questo processo si ripete molte volte, perché un chip è fatto di moltissimi layer.

E qui entra in gioco la dimensione: più piccoli sono i dettagli che riesco a “stampare”, più transistor posso mettere nella stessa area. Più transistor nello stesso spazio significa due cose: a parità di energia posso fare più calcolo, oppure a parità di calcolo posso consumare meno. È il motivo per cui lo “scaling” resta la leva più diretta per aumentare potenza e ridurre consumi.

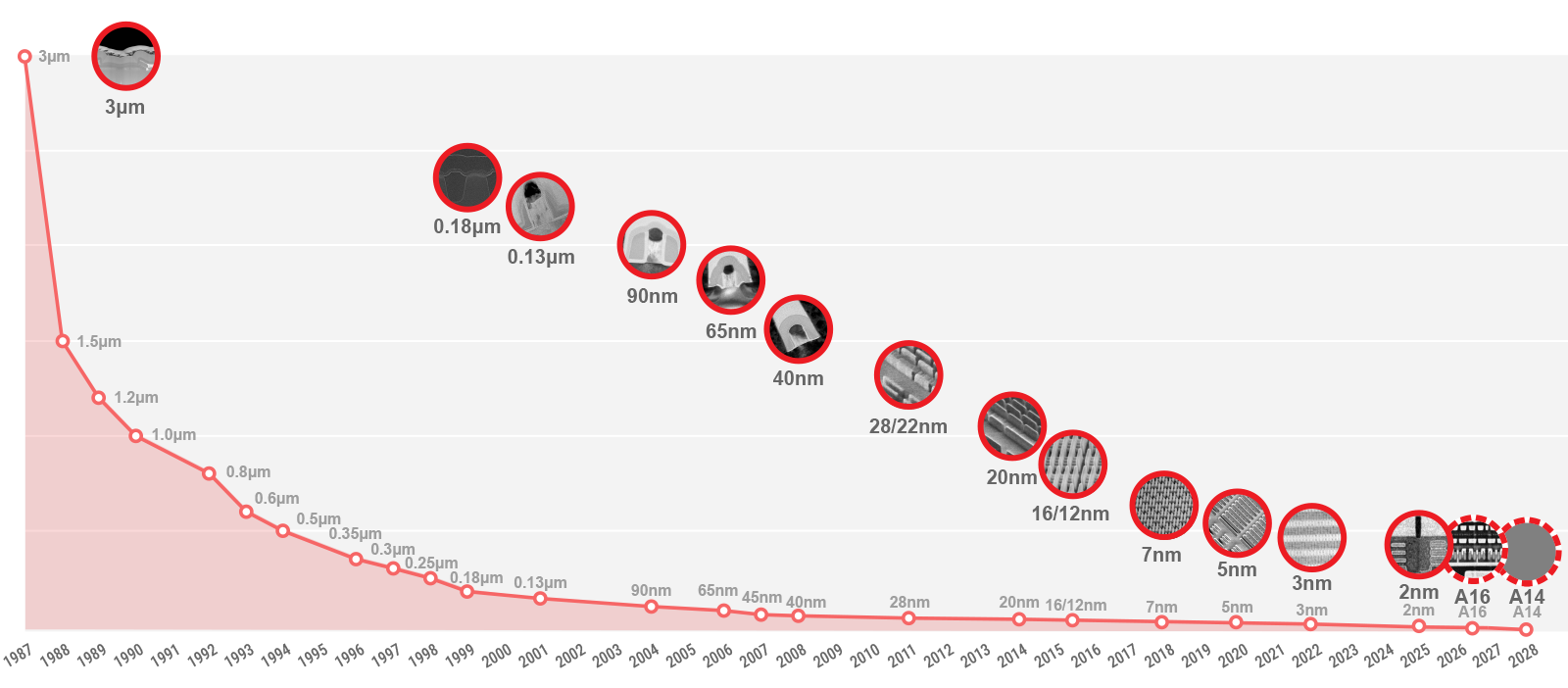

Che cos’è un nanometro e le frontiere

L’unità di misura in questione, su cui si confronta il mondo, è il nanometro, ossia un miliardesimo di metro (10⁻⁹). È un’unità utile perché, su queste scale, i dettagli del chip si misurano in poche decine di atomi. Un paragone che aiuta: le dimensioni “stampate” con le macchine euv possono arrivare a essere circa 10mila volte più sottili di un capello umano, quindi comparabili al diametro dei virus più piccoli.

Vale anche una cautela: i numeri commerciali dei nodi (“2 nm”, “3 nm”) non corrispondono sempre a una singola misura fisica del transistor. Sono etichette di generazione. Ma restano un segnale utile: indicano quanto spinta è la tecnologia di fabbricazione.

Ciò detto, la frontiera “di mercato” oggi è la classe 2 nm. TSMC, il principale produttore materiale di chip, scrive che il suo nodo N2 (2 nm) ha avviato la produzione di volume nel quarto trimestre 2025.

Intel usa una nomenclatura “angstrom”: Intel 18A (18 angstrom = 1,8 nm) e comunica che la tecnologia è diretta verso la produzione ad alto volume nella seconda metà del 2025.

Il passo successivo, dichiarato, è scendere nella fascia 1,4 nm (e dintorni).

TSMC ha presentato A14 (1,4 nm) con un obiettivo di produzione nel 2028. Samsung, nelle sue roadmap ufficiali, indica come obiettivo la produzione a 2 nm nel 2025 e a 1,4 nm nel 2027 (SF1.4), anche se su questi orizzonti i calendari possono slittare per ragioni di resa e costi.

Dentro un’euv: stagno, laser e una “mini supernova” in fab

Come fare a procedere nella miniaturizzazione? Molto della risposta passa dalle macchine euv. Gigantesche: grandi quanto un autobus a due piani e con un peso che può arrivare a oltre 100 tonnellate, con costi fino a 400milioni di dollari. Il motivo di questi grandi numeri è che la luce euv viene assorbita dall’aria: molte parti della macchina lavorano in vuoto e usano specchi specialissimi (non lenti tradizionali), dove il leader è Zeiss.

La parte più sorprendente è la sorgente: all’interno, minuscole gocce di stagno vengono “colpite” da impulsi laser 60.000 volte al secondo; lo stagno diventa un plasma rovente e produce luce euv. La temperatura può arrivare a circa 220.000 gradi Celsius, cioè grosso modo 40 volte la temperatura della superficie del Sole. Un fisico, Bruno La Fontaine del Lawrence Berkeley National Laboratory, la paragona a una “mini supernova” confinata in una camera a vuoto.

Quella luce rimbalza su una serie di specchi che la focalizzano sulla maschera (lo “stencil” del circuito) e poi sul wafer. È una catena delicatissima: basta contaminare gli specchi e l’immagine perde qualità.

Così si capisce perché, per andare oltre, l’industria stia lavorando su più fronti insieme: rendere la “stampa” più fine, ma anche più economica e più stabile.

High-na euv: più dettaglio come in una fotocamera (ma a scala atomica)

Un modo per stampare più piccolo senza cambiare il “colore” della luce è aumentare la numerical aperture (na) del sistema ottico. Il concetto è simile a una fotocamera: un’ottica che “raccoglie” più luce e la focalizza meglio produce immagini più nitide, quindi dettagli più piccoli.

ASML, l’unico produttore di scanner euv, ha dichiarato a fine febbraio 2026 che gli strumenti High-na sono pronti tecnicamente per la produzione ad alto volume: secondo Reuters, hanno processato oltre 500mila wafer con uptime intorno all’80% e hanno un costo nell’ordine di centinaia di milioni a macchina. High-na può ridurre il multipatterning (cioè il numero di passaggi necessari per ottenere lo stesso dettaglio), con benefici su complessità e variabilità di processo.

Sul fronte clienti, Intel Foundry si è posizionata tra gli apripista: ASML e Intel hanno formalizzato l’ordine del sistema Twinscal EXE:5200 con l’obiettivo di portare High-na in manifattura.

Cambiare la lunghezza d’onda: perché “oltre euv” diventa un problema di energia

L’altra leva, oltre alla na, è ridurre la lunghezza d’onda della luce: in generale, luce con lunghezza d’onda più corta permette di stampare dettagli più piccoli. Ma scendere sotto 13,5 nm non è “un aggiornamento”: man mano che la lunghezza d’onda si accorcia, cresce rapidamente la potenza necessaria per generare la luce e diventano più difficili specchi, contaminazione, materiali.

Per questo alcune proposte non cercano di miniaturizzare ulteriormente la sorgente dentro ogni macchina, ma di cambiare architettura: separare la sorgente e trattarla come un’infrastruttura.

Nel 2025 il Dipartimento del Commercio degli Stati Uniti e NIST hanno annunciato una lettera d’intenti (programma CHIPS) con xLight, Inc., startup che sviluppa una sorgente basata su free-electron laser (fel). Nel modello raccontato dai tecnici dell’azienda, l’idea è usare un acceleratore lineare di particelle “utility scale” per produrre un fascio di luce e alimentare più scanner, invece di avere una sorgente per ogni macchinaIl ceo e cto Nicholas Kelez descrive il modello come “light as a service”: le fab pagherebbero la luce come una utility, non tutta la macchina in anticipo.

Il progetto prevede test al complesso Albany Nanotech con NY CREATES. xLight ha Pat Gelsinger (ex ceo di Intel) come executive chairman.

Da una parte quindi la promessa tecnica (sorgente più “pulita” e potenzialmente più efficiente), dall’altra l’ostacolo non tecnico ma industriale: portare un paradigma nuovo in un ecosistema super complesso di produzione chip che ora premia continuità e affidabilità.

La chimica del resist: imec e la ricerca di un processo più “tollerante”

Anche con la migliore ottica, l’immagine finale dipende dal photoresist. A queste scale, la stampa non è solo geometria: è statistica. Pochi fotoni, pochi elettroni secondari, reazioni non uniformi. Il risultato sono difetti casuali e rugosità ai bordi che, in fab, diventano resa più bassa e costi più alti.

Per questo motivo imec (Leuven) lavora su leve di processo molto concrete: a febbraio ha annunciato risultati su una modifica del post-exposure bake che, aumentando la concentrazione di ossigeno, migliorerebbe la “photo-speed” dei metal-oxide resists (mor) del 15–20%, riducendo la dose necessaria e aumentando il throughput.

Dal finfet al nanosheet: cosa cambia con il gate-all-around

Il transistor è un interruttore: più è piccolo, meno energia serve per aprirlo e chiuderlo (in media), ma cresce il rischio che la corrente “sfugga” dove non dovrebbe. Per tenere sotto controllo questo effetto, l’industria ha cambiato forma al dispositivo.

Dopo il finfet, la transizione chiave è il gate-all-around (gaa): invece di “abbracciare” il canale su tre lati, il gate circonda il canale quasi completamente. Questo migliora il controllo e aiuta a ridurre dimensioni e consumi.

Samsung Electronics ha avviato nel 2022 la produzione a 3 nm basata su gaa. TSMC indica per N2 l’adozione di nanosheet e colloca l’avvio della produzione di volume nel quarto trimestre 2025.

Forksheet e cfet: l’impilamento dei transistor come risposta al limite dell’area

Quando i margini per “stringere” in orizzontale si riducono, cresce l’interesse per architetture che comprimono ulteriormente le distanze tra transistor n e p (i due “tipi” complementari di transistor che formano la logica cmos, cioè quasi tutti i chip moderni).

Imec descrive il forksheet come architettura ponte e posiziona i cfet (complementary fet) come candidato per generazioni oltre: l’idea è impilare verticalmente transistor n e p, invece di metterli affiancati. Questo aumenta densità e riduce parte delle distanze interne che consumano energia. La controparte è l’aumento di complessità: integrazione, variabilità e gestione termica diventano più difficili.

Backside power: spostare l’alimentazione “dietro” per liberare spazio e ridurre perdite

Una parte crescente dei consumi non nasce nel transistor, ma nella rete che porta corrente e segnali. Se le “strade” sopra il silicio sono intasate, il chip spreca energia e perde frequenza.

La backside power delivery sposta una parte delle linee di alimentazione sul retro del wafer: sopra restano più risorse per i segnali, e si riduce la resistenza elettrica su alcune tratte.

Intel spinge PowerVia come tecnologia per alleviare colli di bottiglia di interconnect. TSMC ha presentato una logica simile con Super Power Rail (spr) nella tecnologia A16, indicando l’avvio produttivo nella seconda metà del 2026.

Co-packaged optics: Ayar Labs e l’idea di sostituire rame con luce

Nei sistemi AI, una parte pesante dell’energia va nello spostare dati: tra chip, memoria e rete. È qui che si inserisce la fotonica nel package: usare collegamenti ottici per aumentare banda e ridurre energia per bit su certe tratte.

Ayar Labs lavora su co-packaged optics e silicon photonics. A inizio marzo 2026 ha annunciato un round Series E da 500 milioni di dollari guidato da Neuberger Berman e ha indicato come ceo e co-founder Mark Wade.

Packaging 3d: TSMC SoIC e Intel Foveros Direct per ridurre la distanza fisica dei dati

Un modo pragmatico per aumentare “potenza utile” senza dipendere solo dal transistor è avvicinare fisicamente blocchi diversi. Con il packaging avanzato, invece di costruire un chip monolitico enorme, si possono impilare o affiancare die diversi con interconnessioni molto più fitte.

TSMC descrive SoIC come tecnologia di integrazione 3d con pitch “sub-10 µm”. Intel parla di Foveros Direct 3D con hybrid bonding rame-rame a passo sub-10 µm. Per un lettore non tecnico: significa “saldare” due chip faccia a faccia con collegamenti molto più ravvicinati dei microbump tradizionali, riducendo distanza, latenza e una parte dei consumi.

Monolithic 3d: Stanford, MIT, CMU, Penn e SkyWater Technology

C’è poi una variante più ambiziosa: costruire strati attivi uno sopra l’altro sullo stesso die, con processi a bassa temperatura, cioè monolithic 3d.

Il 10 dicembre 2025 Stanford University ha raccontato un prototipo realizzato da un consorzio che include Stanford, Carnegie Mellon University, University of Pennsylvania e MIT, in collaborazione con SkyWater Technology. Il principal investigator citato è Subhasish Mitra (Stanford). L’idea è ridurre drasticamente la distanza tra memoria e compute: meno millimetri di “viaggio” dei dati, meno energia buttata.

Oltre il silicio: nanotubi di carbonio e materiali 2d

Se il silicio dovesse diventare troppo difficile da spingere, le alternative più citate sono i nanotubi di carbonio e i materiali 2d (materiali con spessore atomico).

Nel 2019 un team del MIT guidato da Max M. Shulaker ha pubblicato su Nature il microprocessore RV16X-NANO basato su transistor a nanotubi di carbonio. Imec, sul fronte 2d, discute la possibilità di inserire materiali bidimensionali nei canali di dispositivi avanzati come strada per estendere la roadmap, pur con problemi aperti di integrazione industriale.

Superconduttori: Snowcap Compute e la produzione a 300 mm come test di credibilità

Infine c’è chi prova a cambiare tecnologia di switching per inseguire efficienza: la logica superconduttrice, con il vincolo del raffreddamento criogenico.

A giugno 2025 Reuters ha raccontato il round di Snowcap Compute e ha indicato la squadra fondatrice composta da Mike Lafferty (ceo) e dagli scienziati Anna Herr e Quentin Herr. Sul lato infrastrutturale, NY CREATES descrive attività su dispositivi e processi superconduttivi a scala 300 mm, un passaggio importante perché quella dimensione wafer è lo standard industriale.

Per un lettore non esperto: qui la “potenza” si compra pagando in parte con il freddo. Se l’efficienza del calcolo cresce abbastanza da compensare energia e costi della refrigerazione, la tecnologia diventa credibile per alcuni casi d’uso; altrimenti resta confinata a nicchie.

Geopolitica e filiera: Pechino prova a “costruire la propria ASML”

Queste scelte tecnologiche sono infine accelerate dalla geopolitica. Il 5 marzo 2026 un gruppo di manager e accademici cinesi — tra cui Wang Yangyuan (cofondatore di SMIC), Liu Weiping (presidente di Empyrean), Chen Nanxiang (presidente di YMTC) e Zhao Jinrong (presidente di Naura Technology) — ha chiesto un piano nazionale per costruire un’alternativa domestica ad ASML, sostenendo che la filiera cinese è troppo frammentata e che servono risorse coordinate su eda, wafer e apparecchiature di produzione, con l’euv al centro perché la Cina non può acquistare gli scanner più avanzati.

Nella stessa impostazione rientra l’idea di concentrare gli sforzi sui colli di bottiglia colpiti dai controlli Usa: software di progettazione (eda), wafer e soprattutto apparecchiature di produzione, con l’euv al centro perché Pechino non può importare le macchine di ASML. La cornice è la programmazione 2026-2030 (15° piano quinquennale): l’obiettivo dichiarato è “fare sistema” e ridurre la dispersione di capitali e progetti, anche con aggregazioni tra aziende; non a caso, nelle stesse ore delle “due sessioni” il governo ha indicato la volontà di formalizzare un canale accelerato per operazioni di m&a in tecnologie core.

La Cina è in ritardo di qualche anno, ma con i forti investimenti programmati non lo sarà a lungo. Nel frattempo il mondo prova a portarsi avanti.

Questa partita può ricordare a livello teorico un’altra, quella della physical AI (robotica e dintorni), che pure ci dice come l’innovazione hardware avrà un ruolo crescente nell’innovazione, associata all’AI, nel prossimo futuro.

Ma i progressi nei chip si giocano su frontiere in parte sconosciute nell’attuale fisica, nell’ultra piccolo.

In ballo, se si supererà la barriera dei 2 nanometri, c’è però un premio enorme: la prossima vera evoluzione tecnologica. Con tutte le sue enormi ricadute applicative, economiche, geopolitiche.