L’intelligenza artificiale sta cambiando bersaglio. Dopo due anni in cui l’attenzione si è concentrata soprattutto sull’addestramento dei modelli, il collo di bottiglia si sta spostando sull’inferenza: la fase in cui un modello già addestrato risponde a una richiesta, genera testo, codice, immagini o prende decisioni operative. McKinsey stima che entro il 2030 l’inferenza supererà il training e diventerà il carico dominante nei data center per l’AI, con un peso superiore alla metà del compute AI complessivo e pari a circa il 30-40% della domanda totale dei data center.

Questo cambio di equilibrio richiede nuovi chip, su cui ora si concentra l’industria mondiale. Vecchi e nuovi attori. Il punto è che training e inferenza chiedono cose diverse all’hardware. Addestrare un modello premia la parallelizzazione massiccia, su cui le GPU di Nvidia hanno costruito il proprio successo. Servire milioni di richieste reali, spesso con vincoli di latenza, continuità del contesto e costi per token, premia invece la capacità di muovere dati e pesi del modello in modo efficiente.

Conta molto di più l’accesso veloce alla memoria. È qui che si sta aprendo una nuova gara tra architetture. Già lo studio “AI and Memory Wall”, pubblicato nel 2024 da Amir Gholami e altri ricercatori, prevedeva il problema, di cui ora si affacciano soluzioni industriali.

Indice degli argomenti:

Perché le Gpu non bastano più da sole

Le Gpu restano centrali, ma nell’inferenza generativa mostrano un limite noto: la memoria. Nel lavoro di Gholami e colleghi, il problema viene descritto come memory wall. In sintesi: la potenza di calcolo dei server è cresciuta molto più in fretta della banda disponibile per portare dati da e verso la memoria esterna.

Gli autori stimano che negli ultimi vent’anni le prestazioni di calcolo dei server siano cresciute di circa 3 volte ogni due anni, mentre la banda della dram e quella delle interconnessioni siano salite rispettivamente di circa 1,6 e 1,4 volte nello stesso intervallo. Nei transformer decoder, usati per gran parte degli LLM, la memoria diventa così il vincolo principale nel serving.

Nell’inferenza il sistema deve prima elaborare il prompt e poi generare la risposta token dopo token. Nella fase di generazione, il modello consulta di continuo i propri pesi e i token già prodotti. Se questi dati stanno fuori dal chip, o se devono essere richiamati troppo spesso, il tempo e l’energia spesi per spostarli iniziano a pesare quanto, o più, del calcolo puro.

È il motivo per cui il settore sta cercando chip con più memoria on-chip, percorsi dati più corti oppure architetture che riducono al minimo gli accessi alla memoria esterna.

SRAM, DRAM e SDRAM

Ci sono tre memorie che giocano un ruolo qui.

- La DRAM è memoria dinamica: ha grande capacità e costa meno per bit, ma è più lenta dell’SRAM e richiede refresh periodici.

- La SDRAM è una categoria di DRAM sincronizzata con il clock del sistema; in pratica, quando nei server si parla di DDR4 o DDR5, si sta parlando di forme di DDR SDRAM, quindi sempre di DRAM.

- La SRAM, invece, è un’altra cosa. È molto più veloce, non ha bisogno dello stesso tipo di refresh della DRAM ed è usata vicino ai core di calcolo, dentro il chip, proprio perché riduce i tempi di accesso. Il rovescio della medaglia è che occupa più area di silicio e costa di più. Per questo nei processori AI si tende ad avere poca SRAM on-chip, ma velocissima, e molta DRAM off-chip, ma più lenta. Il problema dell’inferenza nasce quando i modelli sono così grandi da costringere il sistema a uscire continuamente dalla SRAM e andare a pescare nella DRAM.

Ossia: la SRAM è il tavolo di lavoro piccolo ma immediato; la DRAM/SDRAM è il magazzino molto più grande ma meno rapido da raggiungere. Nell’inferenza moderna il processore continua a fare avanti e indietro tra tavolo e magazzino.

Più questi viaggi aumentano, più crescono latenza e consumi.

Nvidia prova a difendere il centro del mercato

Nvidia ha capito che la partita si sta spostando. Il 16 marzo 2026 ha presentato la piattaforma Vera Rubin, che mette insieme Cpu, Gpu, networking, Dpu e rack dedicati all’inferenza con Groq 3 LPX. Nella comunicazione ufficiale l’azienda descrive una piattaforma pensata per coprire training, agentic AI e inferenza in tempo reale attraverso componenti diversi dello stesso sistema.

La mossa dice due cose. La prima: Nvidia non intende lasciare l’inferenza ai concorrenti specializzati. La seconda: anche il leader del mercato sta andando verso sistemi più eterogenei, in cui non c’è un solo chip a fare tutto, ma una catena di componenti dedicati a compiti diversi.

Questo è il segnale più importante della fase che si apre: conta sempre meno il singolo acceleratore, conta sempre di più l’architettura del sistema.

La prima risposta: chip enormi con molta memoria sul wafer

Allo studio ci sono diverse soluzioni, però, segno che il problema è complesso e non è chiaro ancora come affrontarlo. Ma ne va del futuro dell’AI e della sua capacità di mantenere le promesse rivoluzionarie, in diversi ambiti sociali, economici, scientifici.

Una strada tentata è semplice da descrivere e molto difficile da realizzare: costruire chip molto più grandi, con una quota molto più alta di memoria sullo stesso supporto di silicio.

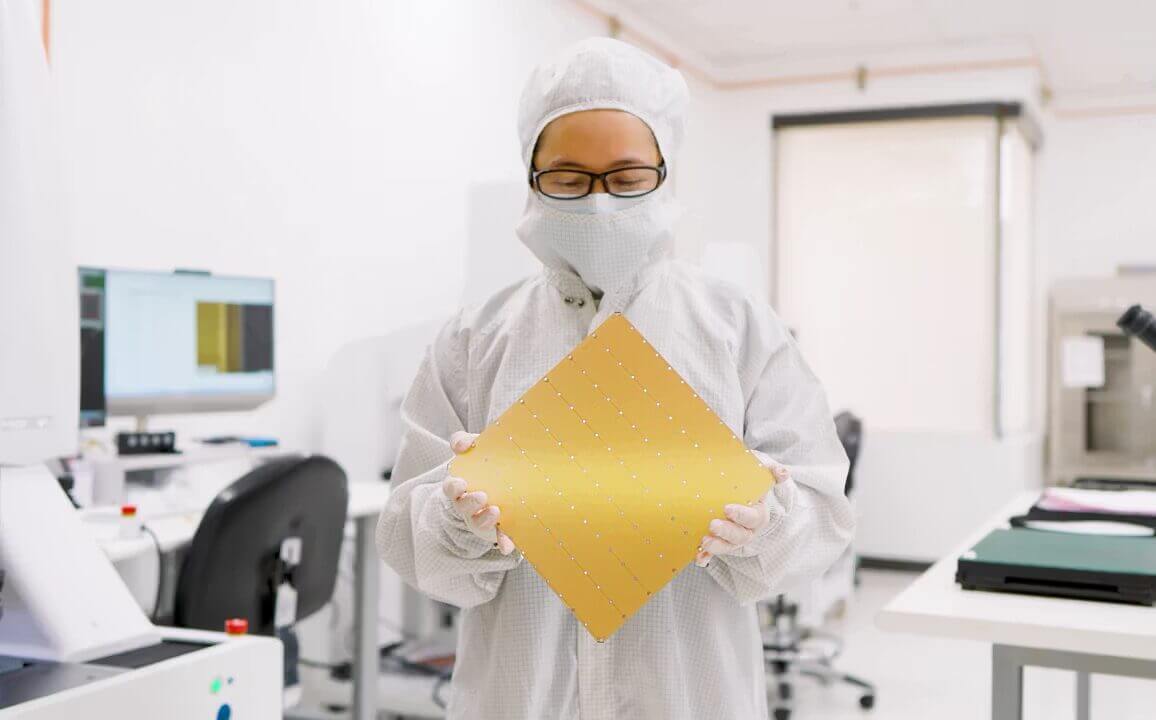

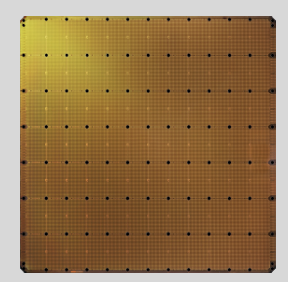

È la scommessa di Cerebras. Il suo Wafer-Scale Engine 3, annunciato nel marzo 2024, integra 4 trilioni di transistor, 900mila core AI e 44 GB di SRAM on-chip su un singolo wafer; Reuters e l’azienda indicano anche 125 petaflops di picco.

Il vantaggio è intuitivo: più dati restano dentro il chip, meno serve andare a pescare fuori. In carichi di inferenza questo può ridurre latenza e consumi. Il limite è altrettanto evidente: quando i modelli crescono molto, non tutto può stare nella SRAM on-chip. Per questo Cerebras continua a usare sistemi più ampi e memoria esterna, ma cerca di spostare dentro il wafer la quota di lavoro più sensibile alla latenza.

Reuters ha anche riferito che l’azienda ha posizionato il WSE-3 in offerte accoppiate a Qualcomm AI 100 Ultra per l’inferenza.

La seconda risposta: cambiare il modo in cui scorrono i dati

Un’altra famiglia di progetti non punta solo a “più chip”, ma a percorsi dati più efficienti. Qui entra in gioco l’idea delle systolic array, usata da anni nei TPU di Google. Google spiegava già nel 2017 che il primo TPU era stato progettato come asic per accelerare la “prediction”, cioè l’inferenza, facendo scorrere i dati in una matrice di calcolo invece di rimandarli ogni volta alla memoria generale.

Su questa linea si muove MatX, startup fondata da ex ingegneri Google, che nel febbraio 2026 ha presentato il chip MatX One. L’azienda lo descrive come basato su una splittable systolic array: una griglia che può essere suddivisa in blocchi più piccoli, così da adattarsi meglio a forme e dimensioni diverse delle operazioni richieste dai modelli linguistici.

Nella descrizione ufficiale, MatX sostiene che il chip combina la bassa latenza dei design “SRAM-first” con il supporto a contesti lunghi tramite hbm.

Bloomberg, secondo la nota aziendale sul round, ha riferito che la società ha raccolto più di 500 milioni di dollari.

L’idea tecnica è interessante perché l’inferenza non è uniforme. Alcune fasi premiano throughput alto, altre premiano latenza bassa e accesso rapido ai dati. Un’architettura più modulare prova a usare meglio il silicio disponibile invece di trattare ogni richiesta come se avesse lo stesso profilo. Questa è una delle direzioni più osservate del mercato.

La terza risposta: unire memoria e calcolo

La proposta più radicale, almeno tra quelle già visibili sul mercato, arriva da d-Matrix. L’azienda parla di digital in-memory compute architecture, una famiglia di soluzioni in cui memoria e calcolo vengono avvicinati il più possibile, fino a convivere nello stesso schema architetturale. L’obiettivo è ridurre i continui trasferimenti di dati che rallentano l’inferenza generativa.

Nel 2024 d-Matrix ha iniziato a spedire il suo primo chip AI, progettato proprio per gestire un gran numero di richieste simultanee in chatbot e generatori video.

L’azienda non si propone come sostituto universale di Nvidia nel training, ma come componente più efficiente per il servizio in produzione.

È un punto importante: molte delle nuove architetture non vogliono vincere ovunque, vogliono vincere nel pezzo del mercato che oggi pesa di più sulla bolletta dei data center, cioè l’inferenza continua e su larga scala.

La quarta risposta: specializzare il chip per un solo algoritmo

C’è poi la strada più aggressiva: costruire un processore che faccia bene una sola cosa. Etched sta seguendo questa via con Sohu, un asic disegnato per i transformer, cioè l’architettura che oggi regge la maggior parte dei modelli linguistici di grandi dimensioni. Nel 2024 che la società ha raccolto 120 milioni di dollari per sviluppare un chip ottimizzato per la fase di inferenza dei transformer.

Il vantaggio di un approccio così è chiaro: togliere dal chip tutto ciò che non serve ad altre reti neurali e concentrare area, energia e software su un solo schema di esecuzione.

Vi sono poi anche tentativi di codificare il modello dentro il layout hardware dei chip, come proposto dall’Accademia di scienze cinesi.

Il rischio di questi approcci così specializzati è l’obsolescenza: il design di un chip richiede molti mesi, mentre gli algoritmi AI cambiano molto più in fretta.

E le Cpu? Nell’inferenza contano più di quanto sembri

Nel racconto pubblico dell’AI, le cpu passano spesso sullo sfondo. È un errore. Le cpu non sono il pezzo “vecchio” del sistema: sono la parte che coordina, prepara, alimenta e in molti casi esegue una quota rilevante del lavoro di inferenza.

Anche la strategia di Nvidia su Vera Rubin va letta così: la piattaforma unisce Cpu, Gpu, networking, storage e acceleratori perché il servizio di inferenza non dipende da una sola categoria di chip.

Tradotto in modo semplice, la cpu fa almeno quattro lavori decisivi. Gestisce la richiesta in ingresso e il networking, coordina il dialogo con Gpu e altri acceleratori, prepara i dati ed esegue una parte del pre e post-processing. In diversi scenari può anche eseguire direttamente l’inferenza, soprattutto su modelli piccoli o medi, carichi batch o applicazioni dove la latenza estrema non è il primo vincolo.

Questa tesi compare in modo esplicito nella documentazione di diversi produttori di Cpu server.

C’è poi un altro aspetto. Nelle installazioni con gpu, la qualità della host Cpu incide sulla latenza finale. Un acceleratore molto potente può essere frenato da Cpu host lente, memoria di sistema insufficiente o cattiva gestione dell’I/O. Per questo motivo la nuova infrastruttura dell’inferenza non sarà fatta di “Gpu contro Cpu”. Sarà fatta di Cpu + acceleratori + rete + software di orchestrazione.

Il vero terreno di scontro è il sistema, non il singolo chip

Le architetture che oggi si stanno progettando per l’inferenza possono essere riassunte in quattro direzioni: chip più grandi e ricchi di SRAM, array di calcolo più flessibili, memoria e calcolo integrati, asic fortemente specializzati. Nessuna di queste, da sola, ha già vinto. Anche perché la competizione non si gioca solo sul silicio. Nvidia insiste su piattaforme complete.

Altri attori più specializzati puntano su collaborazione e integrazione aperta con attori di sistema.

La prossima guerra dei chip si deciderà non tanto sul singolo componente quanto sulla qualità dell’ecosistema software hardware. Da vedere quale prevarrà, di quali player. Se sarà chiuso o aperto.

Se ci sarà un monopolio, un oligopolio o una maggiore apertura di mercato rispetto all’attuale scenario dominato da big tech integrate verticalmente.

Tabella finale: attori e approcci

| Attore | Che cosa sta facendo | Obiettivo tecnico | Punto di forza | Rischio o limite |

|---|---|---|---|---|

| Nvidia | Piattaforma Vera Rubin con cpu, gpu, networking, dpu e rack per inferenza con Groq 3 LPX | Coprire training e inferenza con un’infrastruttura eterogenea | Ecosistema completo hardware-software | Complessità crescente del sistema e costo elevato |

| Cerebras | Wafer-Scale Engine 3 con 900.000 core AI e 44 GB di SRAM on-chip | Ridurre gli accessi alla memoria esterna aumentando la memoria sul wafer | Latenza più bassa nei carichi sensibili alla memoria | La SRAM on-chip non basta da sola per i modelli più grandi |

| MatX | MatX One con splittable systolic array | Adattare meglio il calcolo a carichi diversi tra prefill e decode | Uso più efficiente del silicio | Tecnologia ancora giovane e da validare sul mercato |

| d-Matrix | Architettura di digital in-memory compute per l’inferenza | Ridurre il traffico dati tra memoria e calcolo | Efficienza energetica e bassa latenza nei carichi di serving | Ecosistema meno maturo rispetto al mondo gpu |

| Etched | Sohu, asic specializzato per transformer | Massimizzare l’efficienza su una sola famiglia di modelli | Specializzazione estrema sull’inferenza transformer | Dipendenza dall’attuale centralità dei transformer |

| Cpu di nuova generazione | Cpu server che orchestrano il sistema e, in alcuni casi, eseguono inferenza diretta | Gestire pipeline, dati, rete e carichi piccoli o medi senza acceleratori dedicati | Flessibilità, integrazione, costo totale più basso in molti scenari | Prestazioni inferiori agli acceleratori su modelli molto grandi |